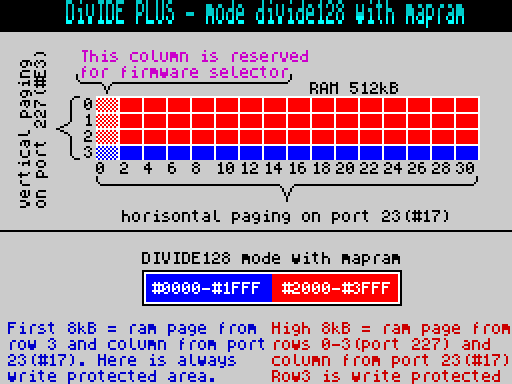

Here is new table for memory paging on DIVIDE PLUS:

Additional info:

- each column can be used as classic 32kB divide mode for one divide system (port 23 select one of 16 possible divide systems/memory)

- one row is used as new 128kB divide memory (port 227 switch between rows)

- this table show memory layout in DIVIDE128 mode with active mapram (active MAPRAM = bit D6 of port 227 is set = rom with divide system is in write protect ram area)

- for DIVIDE128 mode without mapram must be used different table (similar, but not same). Without mapram is rom with divide system in rom chip, and ram pages in rom3 are without write protect. I can add this table later...